# PROGRAMMED DATA PROCESSOR-4 MANUAL

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

# Foreword

This manual is for programmers and users of the Programmed Data Processor-4, a high speed, stored program, digital computer manufactured by the Digital Equipment Corporation. Chapters 2 and 3 contain the detailed information necessary to make use of the machine. Chapter 1 summarizes the machine's electrical and logical design. Chapter 4 presents information helpful in making the electrical connections to inputoutput devices. Appendices provide detailed data which may be helpful in specific programming assignments. Although program examples are given in this document, no attempt has been made to teach programming techniques. However, Appendix 4 explains the meaning and use of special characters used in the programming examples.

Copyright 1962 Digital Equipment Corporation

# Table Of Contents

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | age                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 1: SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                                                                                                                      |

| CHAPTER 2: ARITHMETIC AND CONTROL ELEMENT<br>Functions<br>Control States<br>Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11<br>15                                                                                                               |

| CHAPTER 3: INPUT-OUTPUT EQUIPMENT FUNCTIONS AND PROGRAMMING<br>Input-Output Commands<br>Device Selector<br>Information Collector<br>Information Distributor<br>Input-Output Skip Facility<br>Program Interrupt Control<br>Input-Output Status Instruction<br>Clock/Timer<br>Input-Output Devices<br>Precision CRT Display, Type 30A<br>Light Pen, Type 32<br>Precision CRT Display, Type 30D and Light Pen, Type 32<br>High Speed Analog-to-Digital Converter (Typical Input Device)<br>Low Speed Analog-to-Digital Converter (Typical Input Device)<br>Perforated-Tape Reader<br>Printer-Keyboard and Control, Type 65<br>Perforated-Tape Punch and Control, Type 75<br>Card Reader and Control, Type 41-4<br>Card Punch Control, Type 40-4<br>Automatic Line Printer and Control, Type 62 | 25<br>225<br>226<br>228<br>228<br>229<br>229<br>229<br>230<br>332<br>333<br>334<br>335<br>336<br>338<br>42<br>44<br>46 |

| CHAPTER 4: THE INTERFACE ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                        |

| Appendix 1       Instruction Lists         Appendix 2       Codes         Appendix 3       Read-In Mode Sequence         Appendix 4       Assembly Program         Appendix 5       Multiply and Divide Subroutines         Appendix 6       Programming Aids         Appendix 7       Powers of 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61<br>65<br>67<br>70<br>73                                                                                             |

Typical PDP-4 System

# **CHAPTER 1**

# SYSTEM DESCRIPTION

# Summary

The Digital Equipment Corporation Programmed Data Processor-4 (PDP-4) is designed to be the control element in an information processing system. PDP-4 is a single address, parallel, binary machine with an 18-bit word length using 1's or 2's complement arithmetic. Standard features of the machine are stored program operation, a random access magnetic-core memory, a complete order code, and indirect addressing.

Flexible, high-capacity input-output capabilities of the PDP-4 enable it to operate in conjunction with a variety of peripheral devices, such as perforated-tape readers and punches, punched-card readers and punches, Teletype printer-keyboard, line printers, magnetic tape transports, and analog-to-digital converters.

The machine is completely self-contained, requiring no special power sources, air conditioning, or floor bracing. From a single source of 115-volt, 60-cycle, single-phase power, PDP-4 produces circuit operating dc voltages of -15 volts ( $\pm 1$ ) and +10 volts ( $\pm 1$ ) which are varied for marginal checking. Total power consumption is 900 watts. It is constructed with standard DEC 4000 series system modules and power supplies. Solid-state components and built-in marginal checking facilities insure reliable machine operation.

# System Description

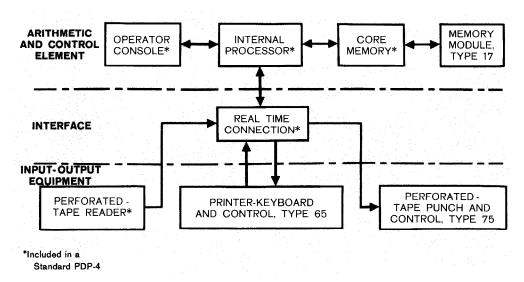

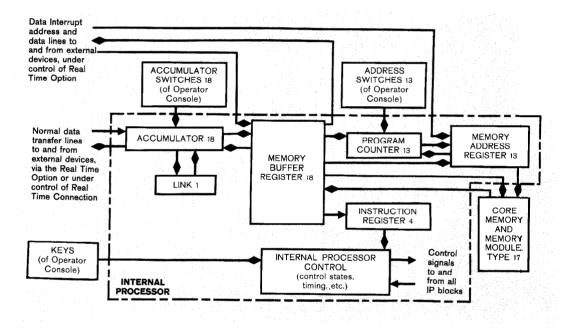

The basic PDP-4 system is shown diagramatically in Figure 1. Three portions of the system are delineated according to function: the Arithmetic and Control Element, the Interface, and the Input-Output Equipment. Information originates not only from peripheral devices but can be entered manually and modified at the Operator Console.

Figure 1 - PDP-4 System with Real-Time Connection

### ARITHMETIC AND CONTROL ELEMENT

The Operator Console, Internal Processor, and Core Memory constitute the Arithmetic and Control Element. The Internal Processor carries out the arithmetic and logical operations and controls the Real-Time Connection and the Core Memory. Binary arithmetic with a fixed point is employed. The optional Extended Arithmetic Control Unit, Type 22, gives PDP-4 a multiply, divide, and arithmetic shifting capability without the use of subroutines.

The Console is used to observe and control the action of the program and the Internal Processor, and to alter the contents of Internal Processor registers. The contents of Core Memory can be examined or new information deposited. All Internal Processor registers are displayed continuously.

Memory capacities of from 1,024 to 32,768 words are available for PDP-4. The cycle time (the time required to read information from memory and rewrite information back into memory) is 8 microseconds. The access time (the time required to read information from memory) is 2 microseconds. In the event of power failure, the contents of the Core Memory remain unaltered. See Chapter 2 for detailed functions of the Arithmetic and Control Element.

### INTERFACE

The Real-Time Connection, furnished as standard equipment, provides communication between the Internal Processor and the Perforated-Tape Reader, the Perforated-Tape Punch and Control, Type 75, and the Printer-

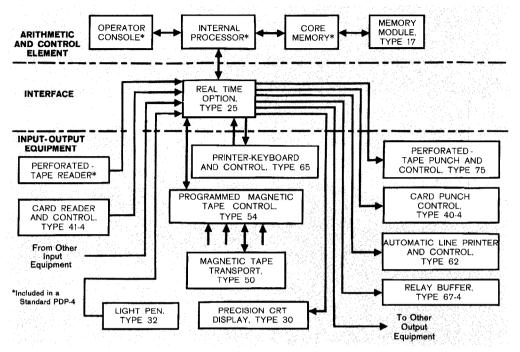

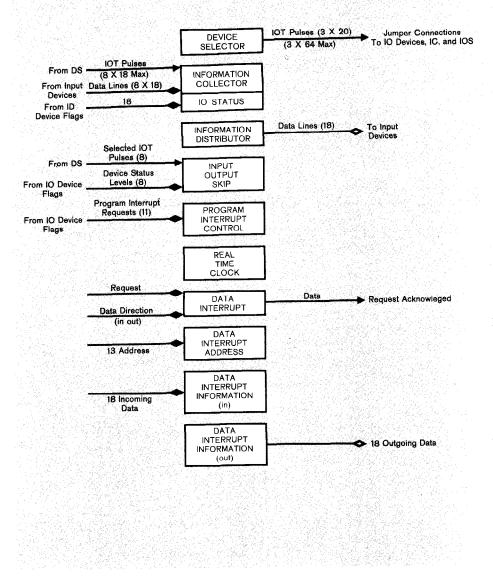

Keyboard and Control, Type 65. The Real-Time Option, Type 25 gives the system the additional capability to operate efficiently over a wide range of information handling rates (from seconds per event to 125,000 words per second) and with a large variety of input-output devices (see Figure 2). The Real-Time Option consists of a Device Selector, an Information Collector, an Information Distributor, an Input-Output Skip connection, a Program Interrupt facility, a Data Interrupt facility, and a Clock/Timer. See Chapter 3 for details of functions.

Figure 2 — PDP-4 System with Real-Time Option

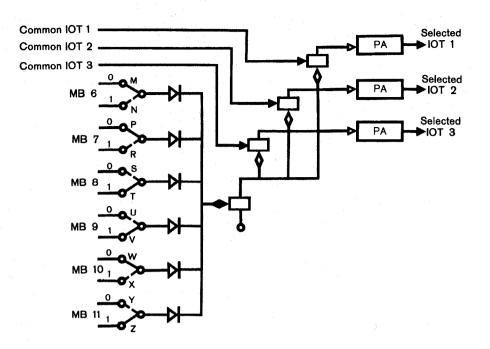

THE DEVICE SELECTOR consists of decoding elements to select and establish the state of an external device when the program issues an input-output transfer instruction. The direction of information transfer (in or out of the Internal Processor) is controlled by signals produced by the Device Selector. Up to 64 input-output devices can be selected and these, in turn, may cause the selection of many more. The standard Device Selector has provisions for twenty selector elements.

THE INFORMATION COLLECTOR receives information from input devices (selected by the Device Selector) and transfers the information to the Internal Processor. Up to 18 bits of information can be collected simultaneously;  $8 \times 18$  bits of information may be collected, broken into variable-sized words.

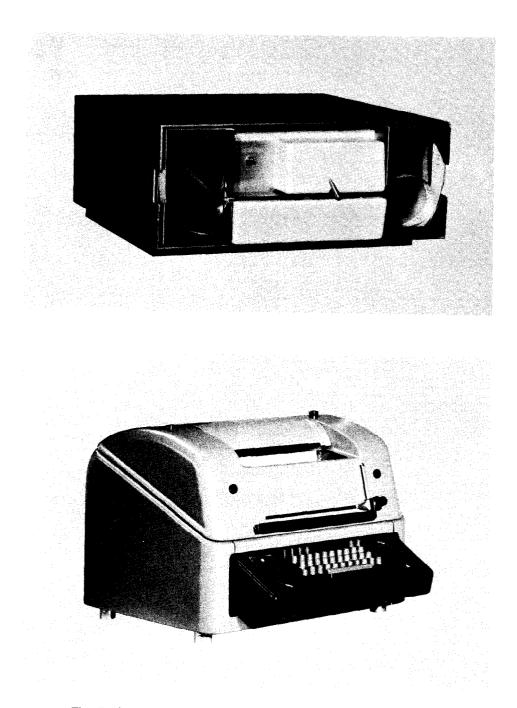

The Perforated-Tape Reader (top) and Printer-Keyboard (bottom).

THE INFORMATION DISTRIBUTOR distributes information from the Internal Processor to all output devices. Only the output device selected (or addressed) by the Device Selector samples and reads in the information contained in the Information Distributor. Up to  $8 \times 18$  bits may be distributed.

THE INPUT-OUTPUT SKIP CONNECTION provides a program skip instruction conditioned by the state of a given input-output device logic line. The instruction following the skip instruction will not be executed if the line is a 1. Eight skip conditions may be sampled.

THE PROGRAM INTERRUPT permits one of 11 lines (conditions) or input-output devices to interrupt the program and initiate a subroutine which may return to the original program when the cause for interruption has been processed. The machine state is preserved during a Program Interrupt. This type of interrupt is suited for information or event rates in the range of 0 to 2,000 cycles per second.

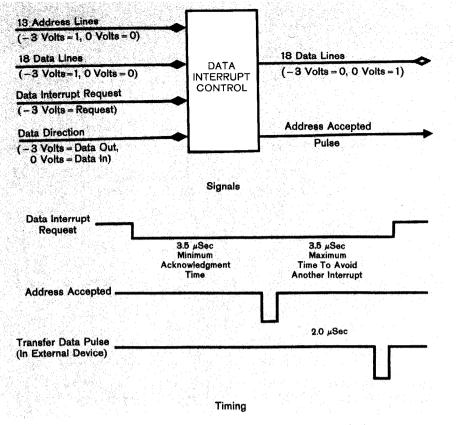

THE DATA INTERRUPT allows a device to automatically interrupt the program and deposit or extract data from the Core Memory at an address specified by the device. The Data Interrupt is suited for high speed information transfers; up to 125,000 18-bit words may be transferred per second.

THE CLOCK/TIMER produces a signal which increments a Core Memory register at a rate of 60 cycles per second. When the register overflows, a Program Interrupt occurs.

#### **INPUT-OUTPUT DEVICES**

All of the input-output devices are optional except the Perforated-Tape Reader.

THE PERFORATED-TAPE READER senses 5-, 7-, or 8-hole perforatedtape at the rate of 300 lines per second. Either one line of tape (alphanumeric) or 3 lines of tape (binary word) may be read.

THE PERFORATED-TAPE PUNCH AND CONTROL, TYPE 75, perforates 5-, 7-, or 8-hole paper tape at a rate of 63.3 lines per second.

THE PRINTER-KEYBOARD AND CONTROL, TYPE 65, includes a Teletype Model KSR-28 Printer and Keyboard with an allowable input or printing rate of ten characters per second. Typed information may be monitored by a program. A program may print information.

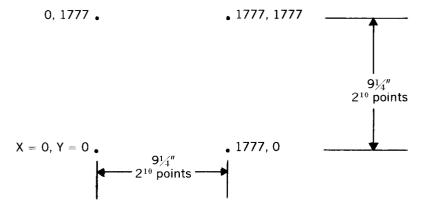

THE PRECISION CRT DISPLAY, TYPE 30, displays data on a 9¼" by 9¼" area. Information is plotted point by point to form either graphical or tabular data. Operation of this device requires the Real-Time Option.

THE LIGHT PEN, TYPE 32, is a photoelectric device which detects information displayed on the Type 30 Visual CRT Display. Upon signal

from the Light Pen, the computer carries out previously programmed instructions. Requires Real-Time Option.

THE 18-BIT RELAY BUFFER, TYPE 67-4, provides contacts which operate devices of higher power rating. The relays have form "D" contacts, which open and close in approximately 3 milliseconds. Requires Real-Time Option.

THE PROGRAMMED MAGNETIC TAPE CONTROL, TYPE 54, controls up to four Magnetic Tape Transports, Type 50. Information is read from or written on the tape. The format on the tape may be programmed to be compatible with IBM tapes having a density of 200, 6 + 1 bit characters per inch. Requires Real-Time Option.

THE MAGNETIC TAPE TRANSPORTS, TYPE 50, are used with the Programmed Magnetic Tape Control, Type 54.

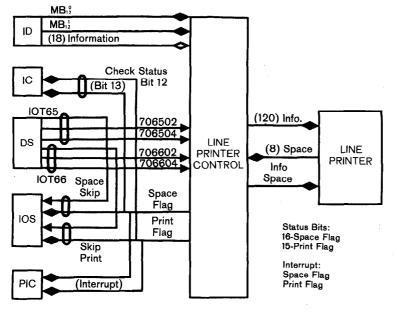

THE AUTOMATIC LINE PRINTER AND CONTROL, TYPE 62, operates at up to 600 lines per minute, 120 columns per line. Each column may print one of 64 characters. Spacing format is controlled by a punched format tape in the Printer. Once a command to print or space is given, the Internal Processor is not required. Approximately one per cent of program running time is required to operate the Line Printer at a 600-line-per-minute rate. Requires Real-Time Option.

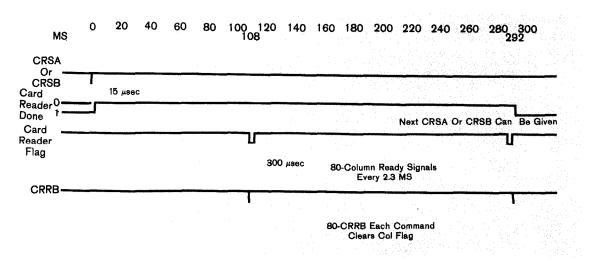

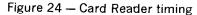

THE CARD READER AND CONTROL, TYPE 41-4, operates at a rate of up to 200 cards per minute. Cards are read column by column. Column information may be read in alpha-numeric or binary mode. The alphanumeric mode converts the 12-bit Hollerith Code of one column into the six-bit binary-coded decimal code with code validity checking. The binary mode reads a 12-bit column directly into the PDP-4. Approximately one per cent of a Card Reader program running time is required to read the 80 columns of information at the 200 cards per minute rate. Requires Real-Time Option.

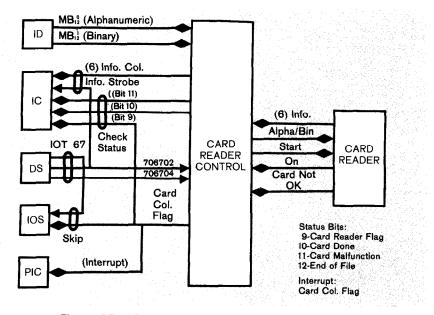

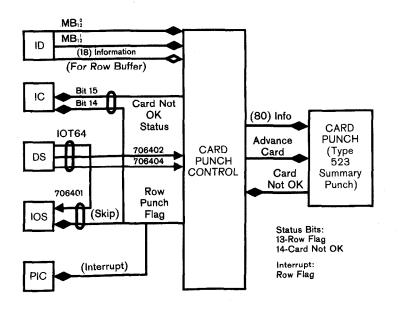

THE CARD PUNCH CONTROL, TYPE 40-4, enables the operation of a standard IBM Type 523 Summary Punch with PDP-4. Cards are punched row by row at a rate of 100 cards per minute. Approximately 0.3 per cent of program running time is required to operate the Card Punch at the 100-card-per-minute rate. Requires Real-Time Option.

### PROGRAMMING AIDS

Several programs are supplied with each PDP-4 to assist the programmer in routine tasks. They include: The PDP-4 Assembly Program, the DDT-4 debugging tape, double-precision floating point routines, maintenance routines, a tape reproducer, punch routines, an octal debugging routine, an algebraic compiler, and a floating point functions program which will enable various functions, such as double precision floating-point sine, to be computed. See Appendix 6.

# **CHAPTER 2**

# ARITHMETIC AND CONTROL ELEMENT

In this chapter the functions of the Arithmetic and Control Element are described in detail. The operations of the machine instructions are explained and listed.

# **Functions**

### INTERNAL PROCESSOR

The Internal Processor performs arithmetic operations, controls memory access, and handles information entering and leaving the machine. It consists of the Information Processor Control, which oversees all activities, and six registers: Accumulator, Link, Memory Buffer, Memory Address, Instruction, and Program Counter. The elements of the Internal Processor are shown within the broken line in Figure 3.

Figure 3 – Arithmetic and Control Element

ACCUMULATOR (AC): Arithmetic operations are performed in this 18-bit register. The AC may be cleared and complemented. Its contents may be rotated right or left with the Link. The contents of the Memory Buffer may be added to the contents of the AC with the result left in the AC. The contents of both these registers may be combined by the logical operations AND and Exclusive OR, the result remaining in the AC. The Inclusive OR may be formed between the AC and the Accumulator Switches on the Operator Console (see below), and the result left in the AC.

The Accumulator also acts as an input-output register. Under normal operation all information transfers between core memory and an external device must pass through the Accumulator.

LINK (L): This is a one-bit register used to extend the arithmetic facility of the Accumulator. In 1's complement arithmetic, the Link is an overflow indicator; in 2's complement it functions as a carry register. The Link may be cleared and complemented and its state sensed independent of the AC. It is included with the AC in rotate operations.

MEMORY BUFFER (MB): All information transferred between Core Memory and the AC, Instruction Register, or Program Counter passes through the MB. Information is read from a memory cell into the MB and rewritten into the cell in one cycle time (8 microseconds). Instructions are brought from memory into the MB to be decoded. The MB serves also as a buffer for information transferred between Core Memory and an external device in a Data Interrupt. The contents of the MB may be incremented by one.

MEMORY ADDRESS REGISTER (MA): The address of the Core Memory cell currently being accessed is contained in the 13-bit MA. Information may enter the MA from the MB, Program Counter, or from an external device operating in a Data Interrupt.

INSTRUCTION REGISTER (IR): This is a 4-bit register which contains the operation code of the instruction currently being performed by the computer. Information enters the IR from the MB.

PROGRAM COUNTER (PC): The program sequence, that is, the order in which instructions are performed, is determined by the PC. This 13-bit register contains the address of the memory cell from which the next instruction will be taken. Information may enter the PC from the MB, MA, or the Address Switches of the Operator Console.

#### MEMORY

The memory contains stored information for processing, and the instructions of the program being run. Memory capacities of from 1,024 to 32,768 words are available in PDP-4. Standard models PDP-4A and PDP-4B come with 1024-word and 4096-word memories, respectively. The two models are identical in all other respects. The smaller memory has a 32 by 32 by 18 core array, the larger a 64 by 64 by 18 core array. A Memory Module Type 17, containing a 64 by 64 by 18 core array may be added to PDP-4B to give it an 8192-word capacity. With the addition of the Magnetic Core Memory Extension Control Type 16, memory modules may be added to build a memory of 32,768 words. Further increase in storage capacity can be gained by adding the Magnetic Drum System Type 24, available in three capacities: 16,384, 32,768, and 65,536 words.

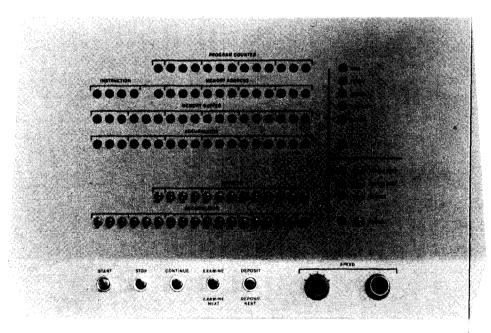

### **OPERATOR CONSOLE**

The Operator Console contains all the switches and controls necessary to run the machine, and lights which indicate the current status of the Internal Processor. The functions of the lights and controls are described in the following tables.

Figure 4 — Operator Console

| Console Switches             | Function                                                                                                                                                                                                                                                                             |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDRESS                      | A group of 13 switches which establishes<br>the memory address for the START, EX-<br>AMINE, and DEPOSIT operations.                                                                                                                                                                  |

| ACCUMULATOR                  | A group of 18 switches, the setting of which<br>determines the word to be placed in memory<br>by the DEPOSIT and DEPOSIT NEXT opera-<br>tions, or to be placed in the AC under<br>program control.                                                                                   |

| POWER                        | Controls the primary power to the computer and all external devices attached to it.                                                                                                                                                                                                  |

| SINGLE STEP                  | Causes the computer to stop at the comple-<br>tion of each memory cycle. Repeated opera-<br>tion of CONTINUE while this switch is on<br>will step the program one cycle at a time.                                                                                                   |

| SINGLE INSTRUCTION           | Causes the computer to stop at the comple-<br>tion of each instruction. Repeated operation<br>of CONTINUE while this switch is on will<br>step the program one instruction at a time.<br>When both switches are on, SINGLE STEP<br>takes precedence over SINGLE INSTRUC-<br>TION.    |

| REPEAT                       | Causes the operations initiated by pressing<br>CONTINUE, EXAMINE NEXT, or DEPOSIT<br>NEXT, to be repeated as long as the key is<br>held on. The rate of repetition is controlled<br>by the setting of the SPEED knobs.                                                               |

| SPEED                        | Two controls that vary the REPEAT interval<br>from approximately 40 microseconds to 8<br>seconds. The left knob is a five-position<br>coarse control, the right knob a continuously<br>variable fine control. For both knobs, slowest<br>speed is obtained in extreme left position. |

| Console Light                | Indication                                                                                                                                                                                                                                                                           |

| ACCUMULATOR                  | The contents of the AC.                                                                                                                                                                                                                                                              |

| MEMORY BUFFER                | The contents of the MB.                                                                                                                                                                                                                                                              |

| LINK                         | The contents of the Link.                                                                                                                                                                                                                                                            |

| MEMORY ADDRESS               | The contents of the MA register.                                                                                                                                                                                                                                                     |

| INSTRUCTION                  | The contents of the IR.                                                                                                                                                                                                                                                              |

| PROGRAM COUNTER              | The contents of the PC.                                                                                                                                                                                                                                                              |

| RUN                          | The computer is executing instructions.                                                                                                                                                                                                                                              |

| FETCH, DEFER, EXECUTE, BREAK | The primary control state of the next mem-<br>ory cycle.                                                                                                                                                                                                                             |

|                              | 14                                                                                                                                                                                                                                                                                   |

| Console Key  | Function                                                                                                                                                                                                                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START        | Starts the processor. The first instruction is<br>taken from memory cell specified by the<br>setting of the ADDRESS switches. The<br>START operation clears the AC and Link,<br>and turns off the Program Interrupt.                                                                                                              |

| STOP         | Stops the processor at the completion of the memory cycle in progress at the time of key operation.                                                                                                                                                                                                                               |

| CONTINUE     | Causes the computer to resume operation<br>from the point at which it was stopped by<br>the last previous operation of STOP or one<br>of the EXAMINE or DEPOSIT keys. Besides<br>the normal off and momentary on positions,<br>CONTINUE has a latched on position ob-<br>tained by raising the key instead of de-<br>pressing it. |

| EXAMINE      | Places the contents of the memory cell<br>specified by the ADDRESS switches in the<br>AC and MB. The contents of the ADDRESS<br>switches appear in the MA. The PC contains<br>the address of the next cell.                                                                                                                       |

| EXAMINE NEXT | Places the contents of the cell specified by<br>the PC in the MB and AC. The C(PC) are<br>incremented by one. The MA contains the<br>address of the register examined.                                                                                                                                                            |

| DEPOSIT      | Deposits the contents of the AC switches in<br>the memory cell specified by the ADDRESS<br>switches. The C(AC switches) remain in the<br>AC and MB. The contents of the ADDRESS<br>switches appear in the MA. The PC contains<br>the address of the next cell.                                                                    |

| DEPOSIT NEXT | Deposits the contents of the AC switches in<br>the memory cell specified by the PC. The<br>C(PC) are then incremented by one. The<br>C(AC), $C(MB)$ , and $C(MA)$ are the same as<br>for DEPOSIT.                                                                                                                                 |

# **Control States**

The PDP-4 operates in one of four primary control states during a memory cycle: Fetch, Defer, Execute, or Break. The next control state is established at the completion of the current one. All states except Break are determined by the instructions themselves.

FETCH: A new instruction is obtained when this state occurs. The contents of the memory cell specified by the PC are placed in the MB,

.

and the instruction part (bits 0-4) of this word are placed in the IR. The C(PC) are then incremented by one.

If a two-cycle instruction is fetched, the following control state will be either Defer or Execute. If a one-cycle instruction is fetched, the operations specified will be performed during the last part of the Fetch cycle. The next state will be Fetch.

DEFER: When bit 4 of a memory reference instruction is a 1, the Defer state is entered to perform the indirect addressing. The process of indirect addressing is often referred to as deferring, in the sense that access to the operand is deferred once to another memory cell. This is why the primary control state in which this operation is performed is called Defer. Bit 4 of a memory reference instruction is referred to interchangeably as the Indirect or the Defer Bit.

EXECUTE: This state is established only when a memory reference instruction is being performed. The contents of the memory cell addressed are brought into the MB, and the operation specified by the C(IR) is performed.

BREAK: When this state is established, the sequence of instructions is broken for a Data Interrupt or a Program Interrupt. In both cases, the break occurs only at the completion of the current instruction.

The Data Interrupt allows information to be transferred between memory and an external device; when this transfer has been completed, the program sequence is resumed from the point of the break. The Program Interrupt causes the sequence to be altered. The C(PC) and the C(L) are stored in location 0000 and the program continues from location 0001.

# Instructions

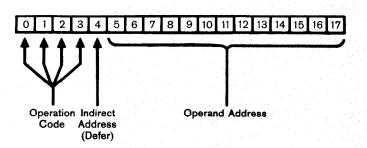

The instruction code is specified by bits 0-3 of a word. There are two types of instructions: Memory Reference and Augmented.

### MEMORY REFERENCE INSTRUCTIONS

The bit assignment of the memory reference instruction is shown in Figure 5. Bits 0-3 determine the operation to be performed. Bits 5-17 specify the address of the memory cell containing the operand. If bit 4 is a 1, then indirect addressing occurs. In the following discussion, i is the mnemonic symbol used to indicate indirect addressing.

#### Figure 5 — Memory reference instruction format

#### INDIRECT ADDRESSING

When indirect addressing is specified, the address part (bits 5-17) of a memory reference instruction is interpreted as the address of a cell containing not the operand, but the address of the operand. Consider the instruction add A. Normally, A is interpreted as the address of the cell containing the quantity be be added to the AC. Thus, if cell 100 contains the number 576, the instruction

add 100

will cause the quantity 576 to be added to the AC. Now suppose that cell 576 contains the number 1135. The instruction

add i 100

(where i signifies indirect addressing) will cause the computer to take the number 576, which is in cell 100, as the effective address of the instruction, and the number in cell 576 as the operand. Hence this instruction will result in the quantity 1135 being added to the AC.

If, when indirect addressing is indicated, the memory cell addressed by the instruction is one of those in locations 10-17, the contents of that cell are incremented by one and the result taken as the effective address. This feature is called auto-indexing. If memory cell 12 contains the number 200, the instruction

add i 12

will cause the number in cell 200 + 1 to be added to the AC.

#### 1'S COMPLEMENT ARITHMETIC

When two numbers are added together in 1's complement arithmetic (see add instruction in following table), a 1 carried out of the high-order position will be added to the low-order digit, as follows:

$\underbrace{\begin{array}{c}110101001100011\\011001010111101\\\hline\\001110100100000\\\hline\\\hline\\001110100100001\end{array}}$

Since bit 0 of a word is used for the sign of a number, the largest positive number that can be represented is  $2^{17} - 1$ . If, in 1's complement addition, the addends are of like sign and the sign of the sum is different, overflow is said to have occurred and the Link is set to 1.

## 2'S COMPLEMENT ARITHMETIC

In 2's complement addition (see tad instruction), a carry out of the highorder bit is not added into the low order position. Instead, if a carry occurs, the Link is complemented. The signs of the addends and sum are not examined. Two's complement addition is used primarily in multiple precision arithmetic.

All memory reference instructions require an Execute cycle (see Control States above) to transfer data between Core Memory and the MB and execute the instruction. When indirect addressing is specified, an extra cycle is required to determine the effective address. The jmp instruction, while it requires an address, does not require an operand; an Execute cycle is thus not needed, and the instruction is performed in only one cycle.

### MEMORY REFERENCE INSTRUCTIONS

#### Explanation of Special Terms

| C(A)<br>A => B<br>Y <sub>1-4</sub><br>Y <sub>j</sub> | A replaces<br>bits 1 - 4 o<br>a given bit | В              | → | exclusive OR<br>inclusive OR<br>AND<br>1's complement of A |  |

|------------------------------------------------------|-------------------------------------------|----------------|---|------------------------------------------------------------|--|

| MNEMONIC<br>SYMBOL                                   | OCTAL<br>CODE<br>(BITS 0-3)               | TIME<br>(μsec) |   | OPERATION                                                  |  |

| (BITS 0-3) | (µsec)         | OPERATION                                                                                                                                                                                                                                                     |

|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20         | 16             | Load AC. The C(Y) are loaded into the AC.<br>The previous C(AC) are lost.<br>C(Y) => C(AC).                                                                                                                                                                   |

| 04         | 16             | Deposit AC. The C(AC) are deposited in<br>the memory cell at location Y. The previous<br>C(Y) are lost; the C(AC) are unchanged.<br>C(AC) => C(Y).                                                                                                            |

| 14         | 16             | Deposit Zero in Memory. Zero is deposited<br>in memory cell Y. The original C(Y) are<br>lost. The AC is unaffected by this operation.<br>0 => C(Y).                                                                                                           |

| 30         | 16             | Add (1's complement). The C(Y) are added<br>to the C(AC) in 1's complement arithmetic.<br>The result is left in the AC and the original<br>C(AC) are lost. The C(Y) are unchanged.<br>The Link is set to 1 on overflow. (See text).<br>C(Y) + C(AC) => C(AC). |

|            | 20<br>04<br>14 | 20 16<br>04 16<br>14 16                                                                                                                                                                                                                                       |

| MNEMONIC<br>SYMBOL | OCTAL<br>CODE<br>(BITS 0-3) | TIME<br>(μsec) | OI                                                                                                                                                                           | PERATIO                                                                | N                                                                                             |

|--------------------|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| tad Y              | 34                          | 16             | Two's compleme<br>added to the Carithmetic. The r<br>the original C(AC<br>unchanged. A car<br>plements the Lin<br>C(Y) + C(AC) =>                                            | (AC) in 2<br>esult is le<br>C) are los<br>arry out o<br>k.             | 2's complement<br>ift in the AC and<br>st. The C(Y) are                                       |

| xor Y              | 24                          | 16             | Exclusive OR. The clusive OR is performed and the C(AC). The and the original (are unchanged, compared independent) $\lor$ C(Y <sub>j</sub> ) $\lor$ C(AC <sub>j</sub> ) = 2 | ormed be<br>the result in<br>C(AC) are<br>Correspondently.<br>> C(AC). | etween the C(Y)<br>is left in the AC<br>is lost. The C(Y)                                     |

|                    |                             |                |                                                                                                                                                                              | ixample                                                                |                                                                                               |

|                    |                             |                | C(AC); original<br>0<br>0<br>1<br>1<br>1                                                                                                                                     | C(Y);<br>0<br>1<br>0<br>1                                              | C(AC); final<br>0<br>1<br>1<br>0                                                              |

| and Y              | 50                          | 16             | AND. The logical<br>formed between $T$<br>The result is left<br>inal C(AC) are I<br>changed. Correspared independen<br>C(Y <sub>i</sub> ) $\land$ C(AC <sub>i</sub> ) =>     | the C(Y)<br>in the AC<br>ost. The<br>ponding<br>ntly.                  | and the C(AC).<br>C, and the orig-<br>C(Y) are un-                                            |

|                    |                             |                | E                                                                                                                                                                            | xample                                                                 |                                                                                               |

|                    |                             | -              | C(AC); original                                                                                                                                                              | <b>C(Y)</b> <sub>i</sub>                                               | C(AC); final                                                                                  |

|                    |                             |                | 0<br>0<br>1<br>1                                                                                                                                                             | 0<br>1<br>0<br>1                                                       | 0<br>0<br>0<br>1                                                                              |

| sad Y              | 54                          | 16             | Skip if AC is Dif<br>are compared wi<br>bers are the sam<br>to the next inst<br>are different, the<br>ped. The C(AC)<br>changed.<br>If C(AC) $\neq$ C(Y) th                  | th the C(,<br>e, the cor<br>ruction.<br>e next ins<br>and the          | AC). If the num-<br>nputer proceeds<br>If the numbers<br>struction is skip-<br>e C(Y) are un- |

| MNEMONIC<br>SYMBOL | OCTAL<br>CODE<br>(BITS 0-3) | TIME<br>(µsec) | OPERATION                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| isz Y              | 44                          | 16             | Index and Skip if Zero. The C(Y) are in-<br>cremented by one in 2's complement<br>arithmetic. If the result is 0, the next<br>instruction is skipped. If not, the com-<br>puter proceeds to the next instruction.<br>The C(AC) are unaffected.<br>C(Y) + 1 => C(Y).<br>If result = 0, $C(PC) + 1 => C(PC)$ . |

| jmp Y              | 60                          | 8              | Jump to Y. The next instruction to be executed is taken from memory cell Y. $Y => C(PC)$ .                                                                                                                                                                                                                   |

| jms Y              | 10                          | 16             | Jump to Subroutine. The C(PC) and the C(L) are deposited in memory cell Y. The next instruction is taken from cell Y + 1.<br>$C(L) => C(Y_0)$ . $0 => C(Y_{1-4})$ .<br>$C(PC) => C(Y_{5-17})$ . Y + 1 => C(PC).                                                                                              |

| cal                | 00                          | 16             | Call Subroutine. The address portion of<br>this instruction is ignored. The action is<br>identical to jms 20. The instruction cal i is<br>equivalent to jms i 20.                                                                                                                                            |

| xct Y              | 40                          | of in-         | Execute. The instruction in memory cell Y will be executed. The computer will act as if the instruction located in Y were in the place of the xct.                                                                                                                                                           |

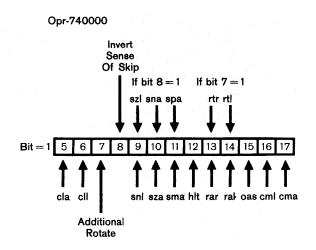

### AUGMENTED INSTRUCTIONS

None of the augmented instructions require a memory reference. Bits 4–17 of an augmented instruction are used to specify operations, many of which may be combined in a single instruction. There are three classes of augmented instructions:

- a. Operate class: includes operations on the AC and Link, the skip group, and the halt instruction.

- b. The special instruction, law.

- c. Input-output transfer class: includes all the instructions which initiate transfers of information between the Internal Processor and an external device and those that sense the status of the devices.

#### OPERATE CLASS

The instructions of the Operate class require one cycle for their execution. The octal code (bits 0–3) for this class is 74. The operations specified by bits 4–17 are called micro-instructions. The functions of each micro-instruction are described in the following table. The Event Time indicates when the operation is performed in the course of the cycle. Times 0, 1, and 2 occur in that order in the latter part of the cycle.

Except for the restrictions indicated at the end of the table, microinstructions may be combined in a single instruction. The bit assignment of the Operate class micro-instructions is shown in Figure 6.

Figure 6 — Operate class instruction — bit assignment

| MNEMONIC<br>SYMBOL | OCTAL<br>CODE | EVENT<br>TIME | OPERATION                                                                                                                    |

|--------------------|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------|

| opr                | 740000        |               | Operate. Indicates the Operate class. When used alone, performs no operation; the computer proceeds to the next instruction. |

| cla                | 750000        | 2             | Clear AC. The AC is cleared to 0. $0 => C(AC)$ .                                                                             |

| cma                | 740001        | 3             | Complement AC. Each bit of the AC is complemented.<br>$\overline{C(AC)} = > C(AC).$                                          |

| cll                | 744000        | 2             | Clear Link. Link is set to 0. $0 => C(L)$ .                                                                                  |

| cml                | 740002        | 3             | Complement Link. $\widetilde{C(L)} => C(L)$ .                                                                                |

| MNEMONIC<br>SYMBOL | OCTAL<br>CODE | EVENT<br>TIME | OPER                                                                                                                                             | ATION             | l                               |

|--------------------|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------|

| ral                | 740010        | 3             | Rotate AC Left. The C(AC) and the C(L) are<br>rotated left one place.<br>$C(AC_i) => C(AC_{i-1})$<br>$C(AC_0) => C(L)$ . $C(L) => C(AC_{17})$    |                   |                                 |

| rtl                | 742010        | 2, 3          | Rotate Two places Left. Equivalent to two successive ral's.                                                                                      |                   |                                 |

| rar                | 740020        | 3             | Rotate AC Right. The C(AC) and the C(L) are<br>rotated one place right.<br>$C(AC_i) => C(AC_{i-1})$<br>$C(L) => C(AC_0)$<br>$C(AC_{17}) => C(L)$ |                   |                                 |

| rtr                | 742020        | 2, 3          | Rotate Two Places Right. Action taken is equivalent to two successive rar's.                                                                     |                   |                                 |

| oas                | 740004        | 3             | OR AC Switches. Th C(AC) and the C(AC synchrony AC. A switch up is in C(AC Switches) $\lor$ C(A                                                  | witche:<br>terpre | s) is placed in the ted as a 1. |

|                    |               |               | Exar                                                                                                                                             | nple              |                                 |

|                    |               |               | C(AC); original                                                                                                                                  | (Y)i              | C(AC); final                    |

|                    |               |               | 0<br>0<br>1<br>1                                                                                                                                 | 0<br>1<br>0<br>1  | 0<br>1<br>1<br>1                |

| sma                | 740100        | 1             | Skip if Minus AC. If t<br>next instruction is skip<br>If $AC_0 = 1$ , then C(PC)                                                                 | ped.              |                                 |

| spa                | 741100        | 1             | Skip if Plus AC. If the                                                                                                                          | AC is r           | ositive, the next               |

| spa | 741100 | 1 | Skip if Plus AC. If the AC is positive, the next instruction is skipped.<br>If $AC_0 = 0$ , then $C(PC) + 1 => C(PC)$ . |

|-----|--------|---|-------------------------------------------------------------------------------------------------------------------------|

| sza | 740200 | 1 | Skip if Zero AC. If C(AC) are 0, the next in-<br>struction is skipped.                                                  |

|     |        |   | if $C(AC) = 0$ , then $C(PC) + 1 => C(PC)$ .                         |

|-----|--------|---|----------------------------------------------------------------------|

| sna | 741200 | 1 | Skip if Non-zero AC.<br>If C(AC) $\neq$ 0, then C(PC) $+1 =>$ C(PC). |

| MNEMONIC<br>SYMBOL | OCTAL<br>CODE | EVENT<br>TIME                                                | OPERATION                                                                                                          |

|--------------------|---------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| snl                | 740400        | 1                                                            | Skip if Non-zero Link. If C(L) is 1, the next instruction is skipped.<br>If C(L) $\neq$ 0, then C(PC) +1 => C(PC). |

| szl                | 741400        | 1                                                            | Skip if Zero Link.<br>If C(L) = 0, then C(PC) $+ 1 =>$ C(PC).                                                      |

| hlt                | 740040        | immedi-<br>ately after<br>the compl<br>tion of the<br>cycle. | le-                                                                                                                |

If skips are combined in a single instruction, the Inclusive OR of the conditions to be met will determine the skip. For instance, if both sza and snl are indicated (octal code 740600), the next instruction will be skipped if either the AC is zero or the Link is non-zero, or both.

If ral or rar is specified, cma, cml, oas may not be specified, and conversely. If rtl or rtr is specified, cma, cml, cla, cll, oas may not be specified, and conversely.

### THE INSTRUCTION, law

The octal code for this instruction is 760000. Bits 5-17 are used to specify a quantity to be placed in the AC. The effect of the law instruction is to place itself in the AC.

law Y 76  $8 \mu \text{sec}$  Load AC With law Y.

### INPUT-OUTPUT TRANSFER CLASS

The instructions in this class are used to effect information transfers between the Internal Processor and external devices, via the Interface.

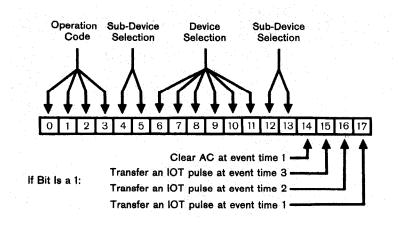

iot 760000 8  $\mu$ sec Input-Output Transfer. Bits 4-13 of an iot instruction determine the device and subdevice to be selected. The presence of a 1 in bit 14 will cause the AC to be cleared at Event time 1. Bits 15-17 determine when pulses are to be sent to the selected device.

The bit assignment of the iot instruction is shown in Figure 7. The instructions of the iot class are described in Chapter 3.

Figure 7 — Bit assignment for input-output transfer instruction (iot)

# CHAPTER 3

# INPUT-OUTPUT EQUIPMENT FUNCTIONS AND PROGRAMMING

PDP-4 is capable of operating with the ten input-output devices described in Chapter 1 and with a variety of others. The computer can operate with most of the devices simultaneously. The Interface, consisting of the Real-Time Connection or the Real-Time Option, issues commands to the devices, monitors their state of availability, transfers information to them, and receives information from them. Since the Internal Processor can store or read out data much faster than the devices can operate, the Interface and the individual devices provide buffering to minimize the amount of program time consumed in transfers.

The Real-Time Connection, furnished as standard equipment, provides communication between the Internal Processor and the Perforated-Tape Reader, the Perforated-Tape Punch, and the Keyboard-Printer. The Real-Time Option, Type 25, gives the system the additional capability to operate efficiently over a wide range of information handling rates, from seconds per event to 125,000 words per second, and with a large variety of input-output devices. The Real-Time Option consists of the Device Selector, the Information Collector, the Information Distributor, the Input-Output Skip Facility, the Program Interrupt Control, the Data Interrupt Control, and the Clock/Timer (see Figure 8).

The coupling of input-output equipment to PDP-4 is similar for all devices. The electrical characteristics of the coupling are discussed in Chapter 4. The logical functions and programming instructions are given below.

# Input-Output Commands

# DEVICE SELECTOR (DS)

The input-output transfer (iot) augmented instruction causes the Interface to produce pulses which select IO devices and transfer information. Upon receipt of an instruction, the Device Selector in the Interface performs one of the following functions:

(a) Starts a device (e.g.asks for a line of perforated tape to be read and assembled into a word, a card to be moved to a reading or punching station, etc.)

(b) Transfers data from the information buffer of an input device to the AC, through the Information Collector

(c) Transfers information from the AC, through the Information Distributor to the buffer of an output device

(d) Senses the flag(s) associated with a device to determine its availability

(e) Resets the flags. These commands dismiss a device without asking for additional action.

The flags referred to above are signals generated by an external device upon completion of its assigned task. This technique allows the Internal Processor to resume its arithmetic operations after issuing an instruction to a relatively slow input-output device (data rate of less than 20,000 words per second). When a flag is set to 1 by the device, it signifies that:

(a) an output action (punch out, etc.) has been completed; the Arithmetic and Control Element may transmit data to the device.

(b) an input action (card or tape input, etc.) has occurred; information is available for the Arithmetic and Control Element.

(c) an alarm condition exists.

Flags may be sensed, and a program skip take place, using the Output Skip Facility (see below). Flags may be read into the AC using the iors (in-out read status) instruction. Most flags are connected to the Program Interrupt (see below).

The Device Selector selects an input-output device or subdevice according to the address code of the device in bits 4-13 in the iot instruction. It then generates IO pulses at event times 0, 1, and 2 if the appropriate micro-instruction code bits are present in bits 17, 16, and 15. Pulse iot 0 occurs near the end of an iot instruction, followed by iot 1 in 2 microseconds. Pulse iot 2 occurs at the beginning of the next instruction, 1.2 microseconds after iot 1. This timing enables one iot instruction to perform multiple operations.

#### **INFORMATION COLLECTOR (IC)**

The Information Collector enables information to be collected from eight 18-bit word input devices. The AC must contain 0 at the time the inputs are sampled. A word can be broken into smaller words according to the word size requirements of the input device. The program steps for reading the contents of a group of static parallel data bits are:

- cla Clear the AC (AC must equal 0)

- iot Selected device (sample the selected device outputs)

- dac Y Deposit C(AC). The C(AC) are sent to a particular memory cell, Y.

(the first two steps may be microprogrammed together in one instruction)

Figure 8 - Real Time Option, Type 25

### **INFORMATION DISTRIBUTOR (ID)**

The Information Distributor presents the static data contained in the AC to each output device requiring AC information. The devices sample the Information Distributor using the program-controlled pulses from the Device Selector. The program steps for transmitting information from a particular memory cell are:

- lac Y Load the AC with C(Y)

- iot Clear selected output register to prepare for information

- iot transmit The information is sampled and placed in the register of the input-output device.

(the second two steps may be microprogrammed together in one instruction)

#### INPUT-OUTPUT SKIP FACILITY (IOS)

The Input-Output Skip facility enables the program to skip (or branch) according to various external device states. There are eight inputs to the Skip facility. The iot pulses from the Device Selector strobe an input line and if a logic condition is present, the instruction following the iot is skipped. The iot skip pulse must occur at event time 1.

#### PROGRAM INTERRUPT CONTROL (PIC)

The program interrupt allows a logic line state to interrupt the program. It is used to speed the processing of input-output device information, or to allow certain alarm conditions to be sensed by the computer. The interrupt may be enabled or disabled by the program.

When the interrupt occurs, the contents of the Program Counter and the Link are stored in memory location 0 (bits  $0, 5 \dots 17$ ) and an interrupt program begins in memory location 1. This action disables the interrupt mode. The interrupt program is responsible for finding the signal causing the interruption, for removing the condition, and for returning to the original program.

When the condition for interruption is removed, an iot signal to re-enable the Program Interrupt is given, followed by the instruction, jmp indirect 0, or 620000. The interrupt program will then resume. If a Program Interrupt request is waiting, it will be serviced after the 620000 instruction. If a second interruption condition occurs and the interrupt program is running, the signal will have no effect; that is, there is only one level of interruption. The START key disables the Program Interrupt system. The iot instructions for the program interrupt are:

iof - 700002 - Disable the Program Interrupt

ion - 700042 - Enable the Program Interrupt

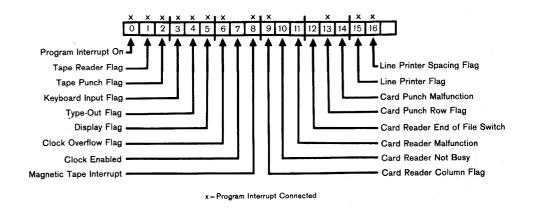

### INPUT-OUTPUT STATUS INSTRUCTION

The iors (in-out read status) instruction, 700314, enables the status of all IO devices to be read into the AC and sampled. Various IO device states are indicated by the presence of a 1 or 0 in the bit positions allocated for that device (see Figure 9).

Figure 9 – Input-Output Status instruction, bit assignment

#### CLOCK/TIMER

The Clock produces a pulse every 1/60 second (16.6 milliseconds) which temporarily interrupts the program (in the same manner as the data interrupt) and a 1 is added to the contents of memory cell 7 using 2's complement addition. If the contents of memory cell 7 are 0 after the addition, the Clock flag is set to 1, which initiates a Program Interrupt if the Interrupt is on. Depressing the START key on the Operator Console clears the Clock flag and disables the Clock. The iot instructions associated with the Clock are:

- csf 700001 Skip the next instruction if the Clock flag is a 1

- cof 700004 Disable the Clock and clear the Clock flag

- con 700044 Enable the Clock and clear the Clock flag

Register 7 is identical to other core memory registers, that is, its contents may be examined or modified. By presetting register 7 to a number, a Program Interrupt will occur when the register overflows after a timed interval.

# **Input-Output Devices**

All of the Input-Output Devices discussed below can be controlled by the Real-Time Option, Type 25. The Real-Time Connection, furnished as standard equipment, provides communication between the Internal Processor and the Perforated-Tape Reader, the Perforated-Tape Punch and Control, and the Printer-Keyboard and Control. All devices except the Perforated-Tape Reader are optional. This section is arranged in the order of increasing complexity of connection.

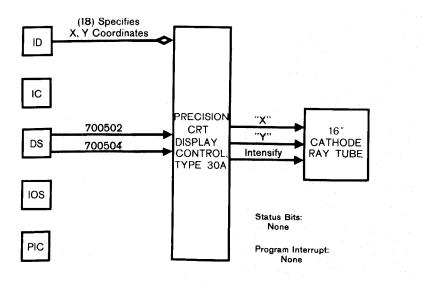

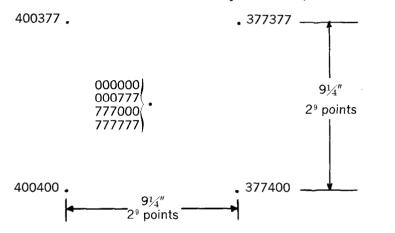

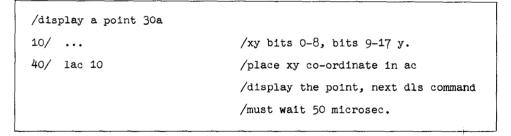

### PRECISION CRT DISPLAY, TYPE 30A

Data points are displayed on a 9¼ inch by 9¼ inch area. Information is plotted point by point to form either graphical or tabular data. Two digital-to-analog converters drive the deflection yokes in the X and Y directions. Data can be plotted at a 20 kc rate, or every 50 miscroseconds.

The program loads the AC with a point to be plotted. Bits 0 through 8 specify the X co-ordinate of the point and Bits 9 through 17 the Y co-ordinate. The C(AC) are then transferred to the Display Buffer. The specifying of the point initiates the plotting of the point on the CRT.

Figure 10 - Precision CRT Display, Type 30A programming logic

The CRT, Type 30A is selected when the numbers 0 and 5 (octal) are specified in bits 8 and 9 respectively, of the iot instruction. The display commands are:

- dls 700506 Load the Display Buffer and select the display. The program loads the Display Buffer from the AC. A point is plotted as specified by the C(Display Buffer). The plotting requires 50 microseconds, after which another dls can be given. The Light Pen flag or Display flag is cleared with dls.

- 700502 Clear the X and Y display buffers.  $0 \Rightarrow C(Display Buffer)$ .

- 700504 -- C(AC) V C(Display Buffer)=>C(Display Buffer). Plot the point specified by the C(Display Buffer).

The points specified in the AC are plotted as unsigned quantities, beginning in the lower left hand corner of the cathode ray tube. The point locations are:

A program sequence is given in PDP-4 Assembly language below. The program begins in register 40, and plots a point, XY, as specified by Core Memory register 10.

PROGRAM SEQUENCE

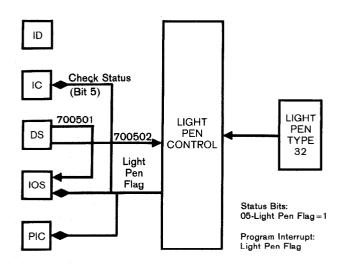

The Light Pen is a photosensitive device which detects the presence of information displayed on a CRT. If the Light Pen is held in front of the CRT at a point displayed, the Display flag will be set to a 1. The Pen is specified by 0 and 5 in bits 8 and 9 of the iot instruction. The commands are:

dsf – 700501 – Skip if Display flag is a 1.

dcf - 700502 - Reset the Display flag to a 0.

The Display flag is connected to bit 5 of the iors instruction, and to the Program Interrupt.

Figure 11 – Light Pen programming logic

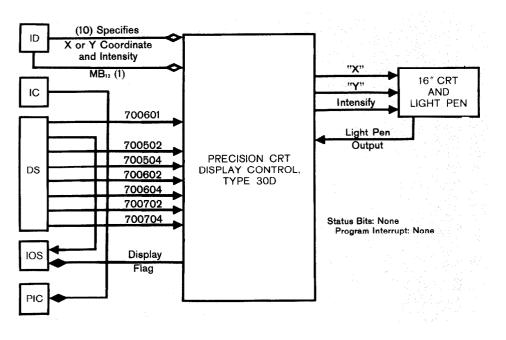

### PRECISION CRT DISPLAY, TYPE 30D AND LIGHT PEN, TYPE 32

The Type 30D display plots points at a 20kc rate. The X and Y co-ordinate buffers (XB and YB) are loaded from the 10 bits,  $AC_{8-17}$ .

The instructions are:

- dsf 700501 Skip if the Display flag is a 1. The Display Flag is set to 1 when the Light Pen senses light.

- dcf 700601 Clear the Display flag.

- dxI 700506 Load the C(XB) with C(AC<sub>8-17</sub>).

- dyl 700606 Load the C(YB) with C(AC<sub>8-17</sub>).

- dxs 700546 Load the C(XB) with C(AC<sub>8-17</sub>). Plot the point: C(XB), C(YB).

- dys 700646 Load the C(YB) with C(AC<sub>8-17</sub>). Plot the point: C(XB), C(YB).

- dlb 700706 Load the Brightness Register with AC bits 15-17. The bits of AC specify the brightness of the points displayed. Clear the Display flag.

- 700502 Clear XB.

- 700504 C(SB)  $\lor$  C(AC) => C(XB). Display a point.

- 700602 Clear YB.

- 700604 C(YB)  $\lor$  C(AC) => C(YB). Display a point.

Figure 12 – Precision CRT Display, Type 30D, and Light Pen, Type 32

The Display flag is connected to the Program Interrupt and to bit 5 of the iors instruction. The co-ordinates of the corners are:

#### **PROGRAM SEQUENCE**

| /dis | play a point 30d |                            |

|------|------------------|----------------------------|

| 10/  | ••               | /x bits 8-17               |

|      | • •              | /y                         |

| 40/  | lac 10           |                            |

|      | dxl              | /load x                    |

|      | lac 11           |                            |

|      | dys              | /load y and plot the point |

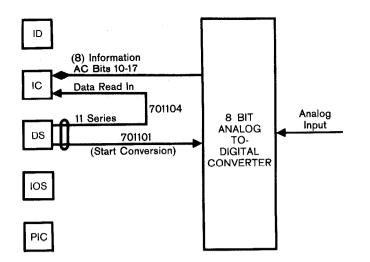

#### HIGH SPEED ANALOG-TO-DIGITAL CONVERTER (TYPICAL INPUT DEVICE)

An analog-to-digital converter with a resolution of 8 bits and a conversion time of 2 microseconds may be connected to the Real-Time Option. The input-output transfer instructions, series 11, for the converter are:

- sci 701115 Sample the analog input. Convert the sampled quantity to digital form and load the AC with the converted number.

- 701101 This micro-instruction starts the converter. In a period of 2 microseconds the converter will form an 8-bit number proportional to the analog input.

- 701104 C(A-D converter)  $\lor$  C(AC) => A(AC).

Figure 13 - High-speed analog-to-digital converter programming logic

A program sequence to sample a function at the input to the converter, and store the result in memory register 10 would be:

#### PROGRAM SEQUENCE

| /anal | .og-to-digital o | converter                   |

|-------|------------------|-----------------------------|

| 10/   |                  | /location of sampled result |

| 42/   | sci              | /places sample in AC        |

|       | dac 10           | /deposit result             |

|       |                  |                             |

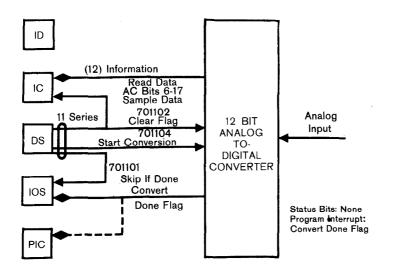

### LOW SPEED ANALOG-TO-DIGITAL CONVERTER (TYPICAL INPUT DEVICE)

An analog-to-digital converter with a resolution of 12 bits and a conversion time of 60 microseconds can be connected to PDP-4. The converter is given an iot command to sample the analog function, and in 60 microseconds the converter will contain a 12-bit number proportional to the input. At the completion of the sample, the converter flag is set to a 1, signifying that the input data is ready.

The contents of the converter buffer are read into the AC with a program command. The action which transfers the information from the converter to the AC also resets the converter flag. An iot skip instruction is used which

skips if the conversion is complete; i.e., the converter flag is a 1. The program instructions, iot series 11, are:

- as f = 701101 Skip if the converter flag is a 1.

- arb 701112 Read converter buffer and clear converter flag.

- ase 701104 Start the converter and clear the converter flag.

- 701102 A micro-instruction which clears the converter flag, and C(converter buffer)  $\lor$  C(AC) => C(AC).

The converter flag might connect to the Program Interrupt.

Figure 14 — Slow-speed analog-to-digital converter programming logic

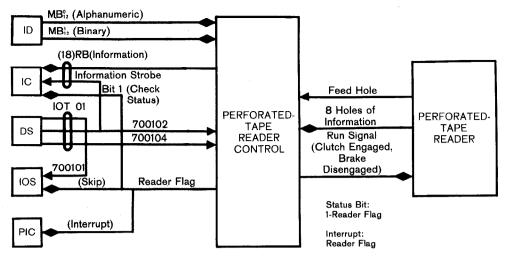

### PERFORATED-TAPE READER

The Tape Reader senses 5-, 7-, or 8-hole perforated-paper (or Mylar) tape photoelectrically at 300 characters (or lines) per second. The Reader control requests Reader movement, assembles data from the Reader into a Reader Buffer (RB), and signals the computer when incoming data is present. Reader tape movement is started by the Reader control request to release the Reader brake and simultaneously engage the clutch.

In addition to the Reader movement control logic, the control unit contains an 18-bit Reader Buffer (RB) which can collect one or three lines from the tape. The C(RB) can be read into the AC. The Reader flag becomes a 1 when a character or word has been assembled in the RB.

Figure 15 – Perforated – Tape Reader programming logic

Figure 16 - Perforated-Tape Reader timing

An alphanumeric character is one line (5, 7, or 8 holes) on tape. A binary word consists of three consecutive characters (18 bits) on tape which have the 8th hole present. Only 8-hole tape is used in the binary mode; the 7th hole is ignored. The first, second, and third six-bit characters are the left, middle, and right thirds, respectively, of the 18-bit word. The reader commands, iot select series 01, are:

- rsf 700101 Skip if Reader flag is a 1, i.e., character or word present.

- rsa 700104 Select Reader and fetch one alphanumeric character from tape. Clear the Reader flag. Reset RB. The character is read into RB bits 10-17. Turn on the Reader flag when character is present.

- rsb 700144 Select Reader and fetch a binary word from tape. Clear the Reader flag. Reset the RB. Fetch the next three characters (with 8th holes present) from perforated tape and place in RB bits 0-5, 6-11, and 12-17. Turn on Reader flag when a word is assembled.

- rrb 700112 Read RB. Clear the Reader flag, and transfer the contents of RB to the AC.

- rcf 700102 Clear the Reader flag. C(RB)  $\lor$  C(AC) => C(AC)

The Reader flag is connected to the Program Interrupt Control and to bit 0 of the iors instruction. Several methods may be used to program the Reader. The following sequence reads a character from tape and places it in the AC. Up to 400 microseconds of computation time are available between the end of the sequence and the next command to read a character or word from tape. The sequence, starting in register 40 is:

#### PROGRAM SEQUENCE

| /perforated-tape reader |                                     |                                           |  |

|-------------------------|-------------------------------------|-------------------------------------------|--|

| 40/                     | 40/ rsa /select reader alphanumeric |                                           |  |

|                         | rsf                                 | /begin loop to look for character arrival |  |

|                         | jmp 41                              | /end loop to look for arrival             |  |

|                         | rrb                                 | /fetch character from reader buffer       |  |

|                         |                                     |                                           |  |

By changing instruction 40 to rsb the sequence would fetch a binary word.

### PRINTER-KEYBOARD AND CONTROL, TYPE 65

The Printer-Keyboard is a Teletype Model 28 KSR (keyboard send-receive) which can print or receive ten characters per second. A five-bit code, given in Appendix 2, represents the characters. The printing (output) and keyboard (input) functions have separate commands and control logic.

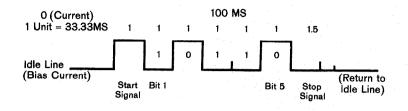

The signals to and from the KSR to the control logic are standard serial, 7.5-unit-code Teletype signals. The signals are: start (1.0 unit), information, bits 1-5 (1.0 unit each), and stop (1.5 units). Figure 17 illustrates the current pattern produced by the binary code 10110.

Figure 17 — Teletype timing of information code 10110

### KEYBOARD

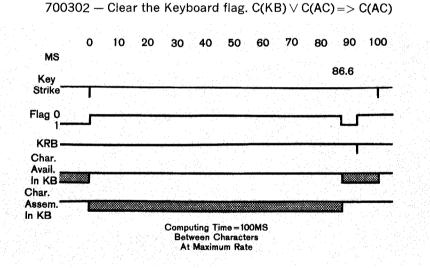

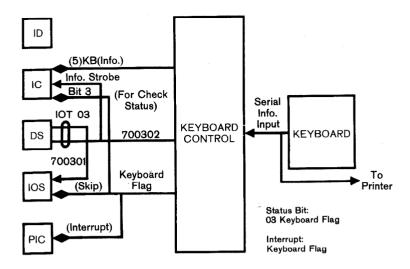

The Keyboard control contains a 5-bit buffer (KB) which holds the code for the last key struck. The Keyboard flag signifies that a character has been typed and its code is present in the Keyboard buffer. The Keyboard flag and Keyboard buffer are cleared each time a character starts to appear on the Teletype line. The Keyboard flag becomes a 1, signifying the buffer is full  $0.5 \pm 0.125$  units after the end of information bit 5, or 86.6 milliseconds after key strike time. The instructions to manipulate the Keyboard are:

ksf - 700301 - Skip if the Keyboard flag is a 1, i.e., character present.

krb – 700312 – Read Keyboard buffer. Clear the Keyboard flag. C(KB)=> C(AC)

Figure 18 – Keyboard timing

Figure 19 — Keyboard programming logic

The Keyboard flag is connected to the Program Interrupt Control and the iors instruction, bit 3. A simple sequence which "listens" for keyboard inputs is:

### PROGRAM SEQUENCE

| 00/ | ksf     | /skip when a character arrives from keyboard |

|-----|---------|----------------------------------------------|

|     | Jmp 400 |                                              |

|     | krb     | /read in the character                       |

The sequence following the listen sequence beginning in 403 may operate for up to 100 + 13.3 milliseconds before returning to listen for the next character without missing the next character. The average computing time between any two characters must be less than 100 milliseconds (for an input rate of 10 characters per second).

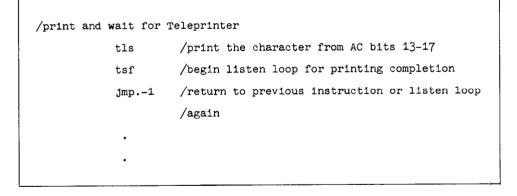

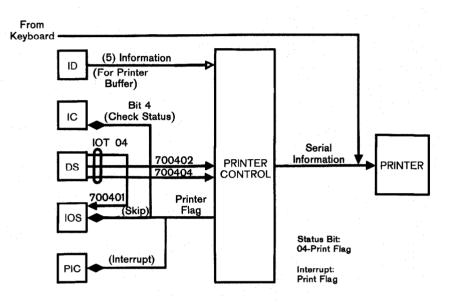

#### TELEPRINTER

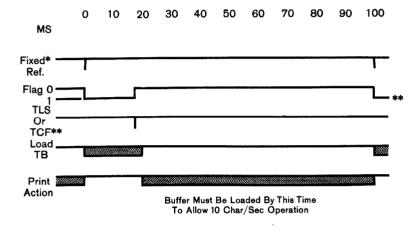

The Teleprinter is given 5 bits of information from AC bits 13 to 17, coding the character to be printed. The teleprinter Buffer (TB) receives this information, transmits it to the Teleprinter serially, and when finished turns on

the Teleprinter flag. The Flag is connected to the Program Interrupt and to bit 4 of the iors instruction. The printing rate is ten characters per second. The instructions for the printer are:

- tsf 700401 Skip if Teleprinter flag is a 1.

- tls 700406 Load the Teleprinter from AC bits 13-17, clear the Teleprinter flag. Select the Teleprinter for printing.

- tcf 700402 Clear the Teleprinter flag.

700404 — C(AC)  $\lor$  C(TB). Print a character.

<sup>\*\*</sup>If TCF, Flag Will Not Come On Until Next TLS Complete \*Determined By Printer

Figure 20 – Printer timing

### **PROGRAM SEQUENCES**

```

/wait for previously printed character completion, then print

tsf /wait loop until previous character printed

jmp.-1 /return to wait loop beginning

tls /print the new character

.

.

```

In the first sequence above, 20 milliseconds of program time is available between that tls and the next one that can be given. In the second sequence, 100 milliseconds of program time is available between that tls and the next one that can be given.

Figure 21 — Printer programming logic

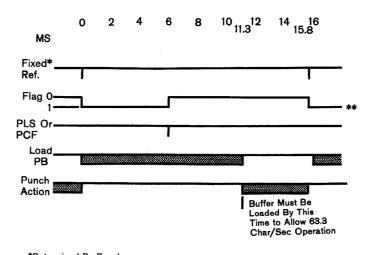

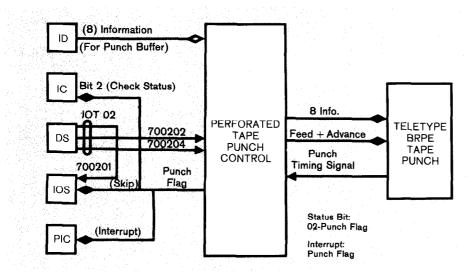

### PERFORATED-TAPE PUNCH AND CONTROL, TYPE 75

The Teletype BRPE paper tape punch perforates 5-, 7-, or 8-hole tape at 63.3 characters (lines) per second. Information to be punched on a line of tape is loaded on an 8-bit buffer (PB) from the AC bits 10 through 17. The Punch flag becomes a 1 at the completion of punching action, signaling that new information may be read into Punch Buffer (PB) (and punching initiated). The Punch flag is connected to the Program Interrupt and to the iors instruction bit 2. The Punch instructions, iot series 02, are:

psf - 700201 - Skip if the Punch flag is a 1.

pcf – 700202 – Clear the Punch flag.

pls – 700206 – Load a character into PB from AC bits 10-17. Clear the Punch flag. Punch the specified character.

700204 – C(PB)  $\lor$  C(AC)=>C(PB). Punch the C(PB).

\*Determined By Punch \*\*PCF Flag Will Not Come On Until Next P Is Complete

Figure 22 — Perforated-Tape Punch timing

**PROGRAM SEQUENCES**

| /punch the contents of AC and wait             |

|------------------------------------------------|

| pls /punches AC 10-17                          |

| psf /wait till done loop beginning             |

| jmp1 /wait till done loop end                  |

| /wait for previous punching, then punch next   |

| psf /wait loop for previous character punching |

| jmp1 /wait loop end                            |

| pls /punch the next character on tape          |

|                                                |

In the first sequence above, 11.3 milliseconds of program time is available between the instruction following the wait loop and the next pls that can be given. In the second sequence, 15.8 milliseconds or more program time is available between the pls and the next time a pls can be given.

Figure 23 — Perforated-Tape Punch programming logic

### CARD READER AND CONTROL, TYPE 41-4